建立時間和保持時間

建立時間(setupTIme)是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘上升沿被打入觸發器;保持時間(hold TIme)是指在觸發器的時鐘信號上升沿到來以后,數據穩定不變的時間,如果保持時間不夠,數據同樣不能被打入觸發器。數據穩定傳輸必須滿足建立和保持時間的要求。

在設計中,當然希望建立時間越短越好,而保持時間呢,也越短越好。也就是說,最好信號在時鐘邊沿到達,而在到達后,馬上被采用,這樣,理論上效率是最好的。當然了,理論而已。

競爭和冒險

PLD內部毛刺產生的原因

我們在使用分立元件設計數字系統時,由于PCB走線時,存在分布電感和電容,所以幾納秒的毛刺將被自然濾除,而在PLD內部決無分布電感和電容,所以在PLD/FPGA設計中,競爭和冒險問題將變的較為突出。這一點用模擬電路的觀點很容易理解,例如在一個延遲鏈條上,加兩個電容,就把這個毛刺給濾掉。

FPGA中的冒險現象

信號在FPGA器件內部通過連線和邏輯單元時,都有一定的延時。延時的大小與連線的長短和邏輯單元的數目有關,同時還受器件的制造工藝、工作電壓、溫度等條件的影響。信號的高低電平轉換也需要一定的過渡時間。由于存在這兩方面因素,多路信號的電平值發生變化時,在信號變化的瞬間,組合邏輯的輸出有先后順序,并不是同時變化,往往會出現一些不正確的尖峰信號,這些尖峰信號稱為毛刺。如果一個組合邏輯電路中有毛刺出現,就說明該電路存在冒險。(與分立元件不同,由于PLD內部不存在寄生電容電感,這些毛刺將被完整的保留并向下一級傳遞,因此毛刺現象在PLD、FPGA設計中尤為突出)我們無法保證所有連線的長度一致,所以輸入信號在輸入端同時變化,但經過PLD內部的走線,到達或門的時間也是不一樣的,毛刺必然產生。可以概括的講,只要輸入信號同時變化,(經過內部走線)組合邏輯必將產生毛刺。將它們的輸出直接連接到時鐘輸入端、清零或置位端口的設計方法是錯誤的,這可能會導致嚴重的后果。所以我們必須檢查設計中所有時鐘、清零和置位等對毛刺敏感的輸入端口,確保輸入不會含有任何毛刺.

如何處理毛刺

(1)使用同步電路,D觸發器:我們可以通過改變設計,破壞毛刺產生的條件,來減少毛刺的發生。例如,在數字電路設計中,常常采用格雷碼計數器取代普通的二進制計數器,這是因為格雷碼計數器的輸出每次只有一位跳變,消除了競爭冒險的發生條件,避免了毛刺的產生。毛刺并不是對所有的輸入都有危害,例如D觸發器的D輸入端,只要毛刺不出現在時鐘的上升沿并且滿足數據的建立和保持時間,就不會對系統造成危害,我們可以說D觸發器的D輸入端對毛刺不敏感。根據這個特性,我們應當在系統中盡可能采用同步電路,這是因為同步電路信號的變化都發生在時鐘沿,只要毛刺不出現在時鐘的沿口并且不滿足數據的建立和保持時間,就不會對系統造成危害。(由于毛刺很短,多為幾納秒,基本上都不可能滿足數據的建立和保持時間)

(2)對信號進行采用得方法,即使用另一個使能信號:以上方法可以大大減少毛刺,但它并不能完全消除毛刺,有時,我們必須手工修改電路來去除毛刺。我們通常使用采樣的方法。一般說來,冒險出現在信號發生電平轉換的時刻,也就是說在輸出信號的建立時間內會發生冒險,而在輸出信號的保持時間內是不會有毛刺信號出現的。如果在輸出信號的保持時間內對其進行采樣,就可以消除毛刺信號的影響。兩種基本的采樣方法:一種方法是在輸出信號的保持時間內,用一定寬度的高電平脈沖與輸出信號做邏輯與運算,由此獲取輸出信號的電平值。上述方法的一個缺點是必須人為的保證sample信號必須在合適的時間中產生,另一種更常見的方法是利用D觸發器的D輸入端對毛刺信號不敏感的特點,在輸出信號的保持時間內,用觸發器讀取組合邏輯的輸出信號,這種方法類似于將異步電路轉化為同步電路。但這會有一個時鐘周期的延遲。

在仿真時,我們也可能會發現在FPGA器件對外輸出引腳上有輸出毛刺,但由于毛刺很短,加上PCB本身的寄生參數,大多數情況下,毛刺通過PCB走線,基本可以自然被慮除,不用再外加阻容濾波。

如前所述,優秀的設計方案,如采用格雷碼計數器,同步電路等,可以大大減少毛刺,但它并不能完全消除毛刺。毛刺并不是對所有輸入都有危害,例如D觸發器的D輸入端,只要毛刺不出現在時鐘的上升沿并且滿足數據的建立和保持時間,就不會對系統造成危害。因此我們可以說D觸發器的D輸入端對毛刺不敏感。但對于D觸發器的時鐘端,置位端,清零端,則都是對毛刺敏感的輸入端,任何一點毛刺就會使系統出錯,但只要認真處理,我們可以把危害降到最低直至消除。下面我們就對幾種具體的信號進行探討。

清除和置位信號

清除和置位信號要求象對待時鐘那樣小心地考慮它們,因為這些信號對毛刺也是非常敏感的。正如使用時鐘那樣,最好的清除和置位是從器件的引腳單直接地驅動。有一個主復位Reset引腳是常用的最好方法,主復位引腳給設計項目中每個觸發器饋送清除或置位信號。幾乎所有PLD器件都有專門的全局清零腳和全局置位。如果必須從器件內產生清除或置位信號,則要按照“門控時鐘”的設計原則去建立這些信號,確保輸入無毛刺。

若采用門控清除或者門控置位,則單個引腳或者觸發器作為清除或置位的源,而有其它信號作為地址或控制線。在清除或復位的有效期間,地址或控制線必須保持穩定

異步輸入信號

按照定義,異步輸入不是總能滿足(它們所饋送的觸發器的)建立和保持時間的要求。因此,異步輸入常常會把錯誤的數據鎖存到觸發器,或者使觸發器進入亞穩定的狀態,在該狀態下,觸發器的輸出不能識別為l或0。如果沒有正確地處理,亞穩性會導致嚴重的系統可靠性問題。

采用附加觸發器同步使能信號的方法可保證不違反計數器的建立時間,從而解決可靠性的問題。雖然同步觸發器仍會感受到亞穩性,但它在下一個時鐘邊沿之前是穩定的。通常,為在EPLD中避免亞穩性問題,決不能把一個異步信號輸出到器件內兩個或更多的觸發器中。同步異步輸入的另一種方法示于圖4.2.16。輸入驅動一個觸發器的時鐘,該觸發器的數據輸入接到Vcc。這個電路對于檢測短于一個時鐘周期的異步事件是有用的。

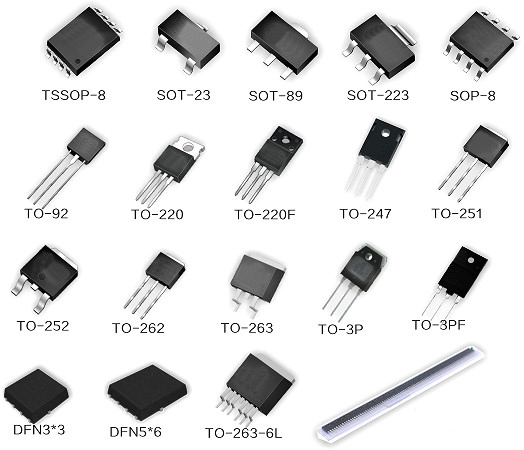

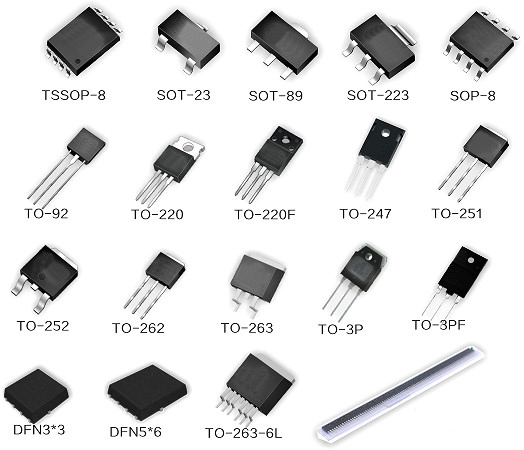

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹